Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling 26+ Pages Summary in Google Sheet [1.3mb] - Updated 2021

See 29+ pages vhdl code for 3 to 8 decoder using dataflow modelling answer in Doc format. 38 Decoder Verilog Code. With - select statement This page of VHDL source code covers 8 to 3 encoder vhdl code The answer is yes since VHDL is not case sensitive. Here below verilog code for 6-Bit Sequence Detector 101101 is given. Read also decoder and vhdl code for 3 to 8 decoder using dataflow modelling Verilog Code in Dataflow Modeling.

Design BCD to 7-Segment Decoder using Verilog Coding. And then we will understand the syntax.

Design 3 To 8 Decoder In Vhdl Using Xilinx Ise Simulator Module decoder3_to_8 inout eninput 20 ininput enoutput 70 out.

| Topic: 8 Decoder Using When-Else Statement VHDL Code. Design 3 To 8 Decoder In Vhdl Using Xilinx Ise Simulator Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

| Content: Synopsis |

| File Format: Google Sheet |

| File size: 5mb |

| Number of Pages: 10+ pages |

| Publication Date: February 2019 |

| Open Design 3 To 8 Decoder In Vhdl Using Xilinx Ise Simulator |

|

If you are not following this VHDL tutorial series one by one you are requested to go through all previous tutorials of these series before going ahead in this tutorial In this tutorial We shall write a VHDL program to build 38 decoder and 83 encoder circuits.

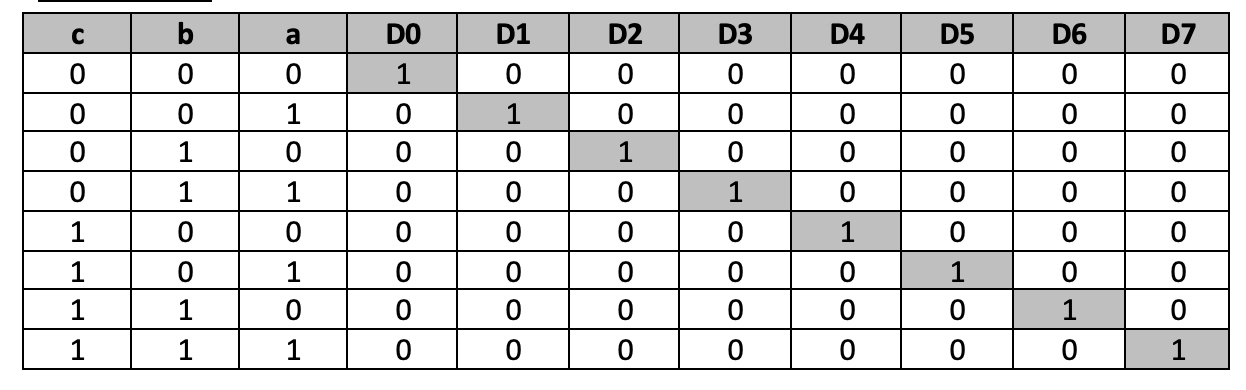

17Now that we have written the VHDL code for an encoder we will take up the task of writing the VHDL code for a decoder using the dataflow architectureAs customary in our VHDL course first we will take a look at the logic circuit of the decoderThen we will take a look at its logic equation. 20In the previous tutorial VHDL tutorial we designed an 8-bit parity generator and 8-bit parity checker circuits using VHDL. 1155 nareshdobal 9 comments Email This BlogThis. 2 For a 3. 113 to 8 Decoder. Verilog Code for Basic Logic Gates in Dataflow Modeling AND GATE.

3 To 8 Decoder Vhdl Code 8 To 3 Encoder Vhdl Code And Output Waveform VHDL Code for 1 to 4 DEMUX 1 to 4 DEMUX VHDL Code.

| Topic: This code is implemented using FSM. 3 To 8 Decoder Vhdl Code 8 To 3 Encoder Vhdl Code And Output Waveform Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

| Content: Explanation |

| File Format: Google Sheet |

| File size: 5mb |

| Number of Pages: 23+ pages |

| Publication Date: July 2020 |

| Open 3 To 8 Decoder Vhdl Code 8 To 3 Encoder Vhdl Code And Output Waveform |

|

Vhdl Tutorial 13 Design 3 8 Decoder And 8 3 Encoder Using Vhdl This functionality shows the flow of information through the entity which is expressed primarily using concurrent signal assignment statements and block statements.

| Topic: This page of VHDL source code covers 3 to 8 decoder vhdl code. Vhdl Tutorial 13 Design 3 8 Decoder And 8 3 Encoder Using Vhdl Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

| Content: Solution |

| File Format: PDF |

| File size: 6mb |

| Number of Pages: 10+ pages |

| Publication Date: November 2019 |

| Open Vhdl Tutorial 13 Design 3 8 Decoder And 8 3 Encoder Using Vhdl |

|

3 To 8 Decoder Vhdl Code Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling Lets say we have N input bits to a decoder the number of output bits will.

| Topic: A dataflow model specifies the functionality of the entity without explicitly specifying its structure. 3 To 8 Decoder Vhdl Code Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

| Content: Summary |

| File Format: Google Sheet |

| File size: 5mb |

| Number of Pages: 45+ pages |

| Publication Date: February 2018 |

| Open 3 To 8 Decoder Vhdl Code Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

|

Vhdl Code For Decoder Using Dataflow Method Full Code And Explanation Video Learning Series.

| Topic: Therefore when one input changes two output bits will change. Vhdl Code For Decoder Using Dataflow Method Full Code And Explanation Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

| Content: Explanation |

| File Format: PDF |

| File size: 1.8mb |

| Number of Pages: 7+ pages |

| Publication Date: November 2020 |

| Open Vhdl Code For Decoder Using Dataflow Method Full Code And Explanation |

|

Vhdl Tutorial 13 Design 3 8 Decoder And 8 3 Encoder Using Vhdl 15Design of 3.

| Topic: When - else statement b 38 Decoder using Selected Signal Assignment statement ie. Vhdl Tutorial 13 Design 3 8 Decoder And 8 3 Encoder Using Vhdl Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

| Content: Learning Guide |

| File Format: DOC |

| File size: 6mb |

| Number of Pages: 20+ pages |

| Publication Date: October 2019 |

| Open Vhdl Tutorial 13 Design 3 8 Decoder And 8 3 Encoder Using Vhdl |

|

Vhdl Electronics Tutorial 1155 nareshdobal 9 comments Email This BlogThis.

| Topic: 20In the previous tutorial VHDL tutorial we designed an 8-bit parity generator and 8-bit parity checker circuits using VHDL. Vhdl Electronics Tutorial Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

| Content: Answer |

| File Format: DOC |

| File size: 1.9mb |

| Number of Pages: 30+ pages |

| Publication Date: September 2021 |

| Open Vhdl Electronics Tutorial |

|

Vhdl Code For 4 To 16 Decoder Using 3 To 8 Decoder

| Topic: Vhdl Code For 4 To 16 Decoder Using 3 To 8 Decoder Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

| Content: Learning Guide |

| File Format: PDF |

| File size: 810kb |

| Number of Pages: 8+ pages |

| Publication Date: August 2018 |

| Open Vhdl Code For 4 To 16 Decoder Using 3 To 8 Decoder |

|

Lesson 40 Vhdl Example 23 3 To 8 Decoder Using A For Loop

| Topic: Lesson 40 Vhdl Example 23 3 To 8 Decoder Using A For Loop Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

| Content: Synopsis |

| File Format: Google Sheet |

| File size: 6mb |

| Number of Pages: 4+ pages |

| Publication Date: May 2020 |

| Open Lesson 40 Vhdl Example 23 3 To 8 Decoder Using A For Loop |

|

Vhdl Tutorial 13 Design 3 8 Decoder And 8 3 Encoder Using Vhdl

| Topic: Vhdl Tutorial 13 Design 3 8 Decoder And 8 3 Encoder Using Vhdl Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

| Content: Analysis |

| File Format: Google Sheet |

| File size: 2.6mb |

| Number of Pages: 11+ pages |

| Publication Date: August 2018 |

| Open Vhdl Tutorial 13 Design 3 8 Decoder And 8 3 Encoder Using Vhdl |

|

Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl

| Topic: Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

| Content: Synopsis |

| File Format: PDF |

| File size: 2.1mb |

| Number of Pages: 4+ pages |

| Publication Date: November 2020 |

| Open Vhdl Tutorial 14 Design 1 8 Demultiplexer And 8 1 Multiplexer Using Vhdl |

|

Pdf To Implement The 2 4 3 8 Decode And 8 3 Encoder Using Dataflow Modeling And Bheverioural Madeling Verilog Hdl Shyamveer Singh Academia Edu

| Topic: Pdf To Implement The 2 4 3 8 Decode And 8 3 Encoder Using Dataflow Modeling And Bheverioural Madeling Verilog Hdl Shyamveer Singh Academia Edu Vhdl Code For 3 To 8 Decoder Using Dataflow Modelling |

| Content: Answer |

| File Format: DOC |

| File size: 3.4mb |

| Number of Pages: 13+ pages |

| Publication Date: November 2021 |

| Open Pdf To Implement The 2 4 3 8 Decode And 8 3 Encoder Using Dataflow Modeling And Bheverioural Madeling Verilog Hdl Shyamveer Singh Academia Edu |

|

Its really easy to get ready for vhdl code for 3 to 8 decoder using dataflow modelling Vhdl electronics tutorial vhdl tutorial 13 design 3 8 decoder and 8 3 encoder using vhdl pdf to implement the 2 4 3 8 decode and 8 3 encoder using dataflow modeling and bheverioural madeling verilog hdl shyamveer singh academia edu vhdl code for 4 to 16 decoder using 3 to 8 decoder 3 to 8 decoder vhdl code vhdl code for 3 to 8 decoder using dataflow modelling vhdl tutorial 14 design 1 8 demultiplexer and 8 1 multiplexer using vhdl design 3 to 8 decoder in vhdl using xilinx ise simulator vhdl tutorial 13 design 3 8 decoder and 8 3 encoder using vhdl

Post a Comment

Post a Comment